#### Tesis Doctoral

# Reconfiguración dinámica de sistemas modulares multi-procesador en dispositivos SoPC

Armando Astarloa Ingeniero Industrial

Mayo de 2005

Director: Dr. Aitzol Zuloaga Izaguirre

A Mirentxu y a Mónica

## **Agradecimientos**

Hace unos años, cuando afronté el reto de hacer esta tesis, me dijeron que era un trabajo personal. Si bien ahora puedo afirmar que, efectivamente, es una labor  $b\'{a}sicamente$  personal, también he de reconocer que, sin la ayuda y los apoyos recibidos, esta tesis se habría convertido en una empresa imposible. Debo agradecer:

A mi Director de tesis, Aitzol. Realmente, tu labor en este trabajo comenzó hace muchos años, cuando yo era alumno interno del Departamento de Electrónica y Telecomunicaciones. Entonces, gracias a tu pasión por la ingeniería y tu actitud de ayuda sin condiciones, sembraste un ingeniero entusiasta de su trabajo y dispuesto a llegar siempre, un poco más lejos. Gracias por la confianza que has puesto en mí.

A los compañeros del grupo de investigación. Tras pasar unos años en la empresa privada, cuando tuve la oportunidad de volver al Departamento, ya como profesor e investigador, no lo dudé. Sabía que me incorporaba a trabajar con excelentes profesionales, pero lo que es más importante para mí, con magníficas personas. Por ello, a mi vuelta, me encontré de nuevo con Aitzol. Con Jose Luis, que con tu dedicación y experiencia, siempre me has prestado toda la ayuda necesaria y más. Con Jaime, dispuesto a la reflexión y al debate. Y con Unai:

A Unai. Debo agradecerte especialmente la ayuda que me has prestado estos años. Las correcciones exhaustivas de esta tesis, los acertados análisis técnicos sobre mis propuestas y ensayos o la aportación de tu experiencia en las publicaciones; que aún siendo todos estos aspectos inestimables, no son más que un apéndice comparado con tu amistad. Tu visión crítica y humana de la vida y de la ingeniería, junto con tu capacidad de dar ánimos en los momentos más difíciles, me han ayudado y me siguen ayudando a afrontar los distintos retos.

A Txus y a Jagoba, mis dos compañeros de despacho en la actualidad. A vosotros debo agradeceros, además de una inestimable ayuda en aspectos técnicos e informáticos, ser unos excelentes compañeros del día a día, que es al fin y al cabo, lo que cuenta.

A todos los alumnos que me han ayudado en el laboratorio. En especial a Sergio, Mikel, Jaime y Eneko. Espero haberos inculcado la ilusión por la investigación y por la ingeniería.

A mis amigos, que sabéis apreciar las aventuras en las que me embarco (como esta tesis), en especial a Amaya, Eva, Iñigo, Javi, Julio, Mikel y Txaro.

A mi familia y en especial, a mi madre. Hemos avanzado estos años contra viento y marea, sin tu fortaleza y tu cariño, nada de esto hubiera sido posible.

A Mónica. Gracias por tu apoyo incondicional; por aceptar que no siempre elija el camino más fácil; por tus consejos; por tu familia; por decidir recorrer el camino conmigo; por tu alegría; en definitiva, por ser como eres.

Gracias a todos.

## **Abstract**

Nowadays, the transistor density of electronic devices allows the integration of complete digital systems on a single integrated circuit. In order to reduce the development time and to face successfully these type of designs, they are made usually using cores. These cores, due to their complexity, often include processors inside. So, in these cases, they are called multi-processor systems.

This level of integration has also been spread to FPGA reconfigurable devices, which have been widely used because of their flexibility. In spite of that, the most common use of the reconfiguration capability is limited to the development stage of the design, to facilitate the debug process and, in some cases, to perform latter upgrades of the digital system.

However, the latest FPGAs allow to modify part of their configuration while the rest of the configured circuit remains running. This ability, called dynamic partial reconfiguration, has an additional interest in the designs that integrate digital systems on a single device. For these situations, the computations made into the chip can also set what context changes must be performed to the modules and apply them. These are the so called auto-reconfigurable systems.

Auto-reconfiguration is a complex operation. To perform it safely in a multi-processor core based system, the FPGA must both technologically admit the reconfiguration and contain a control system to manage the whole process.

This thesis proposes an auto-reconfiguration control system for multi-processor core based systems. First, a general proposal for the control system is presented. It is valid to be integrated into systems that use the most common standard specifications for System-on-a-Chip design. This generalization is described based on a generic multi-processor reconfigurable model, that is used to define the specifications of the different elements that build the control infrastructure. To help the designer to study the viability of the auto-reconfiguration in a design, the infrastructure area and time cost have been modelled and parameterized.

The proposed theoretic system is validated using a specific reconfigurable technology. For this purpose, all the elements specified in the control infrastructure are implemented, and some additional tools are developed to manage multi-processor and multi-context designs. The implemented infrastructure has been applied to three platforms that have been designed to experiment the auto-reconfiguration with the proposed approach. A custom prototype, that admits an exhaustive control of the FPGA configuration sequence, has been built to perform these experiments.

## Laburpena

Gaur egun, gailu elektronikoetan onargarria den dentsitatea hain da handia, ezen zirkuitu integratu bakarrean sistema digital osoen integrazioa posiblea den, System-on-Chip edo SoC deiturikoak. Garapenaren denbora gutxitzeko eta mota honetako diseinuen arrakasta lortzeko, moduluz edo core-z osatuta daude. Modulu hauek, konplexuak izanik, prozesadore batean edo gehiagotan eragina izan ohi dute. Beraz, kasu hauetan, sistema multiprozesadoreak dira.

Integrazio-maila gailu birkonfiguragarrietara (FPGAk nagusiki) ere hedatu egin da. Aukera hau erabilienetariko bat da eskaintzen duen malgutasunagatik. Hala ere, birkonfiguraziorako gaitasuna prototipo faseetara mugatzen da diseinuaren arazketa erraztearren eta, batzuetan, beraren gaurkotzeak egiteko.

Dena den, FPGA berrienek beren konfigurazioaren zati bat moldatzea onartzen dute, zirkuituaren gainontzekoa exekutazen dabilen bitartean. Gaitasun honek, birkonfigurazio partzial dinamikoa deiturikoak, zirkuitu integratu bakarrean eratzen diren moduluz osatutako sistema digitalen diseinuan interes berezia du. Eta, kasu hauetan, txipean egindako prozesaketak moduluen programa edota zirkuituetarako kontestuaren aldaketak erabaki eta aplika ditzake. Mota honetako diseinuei sistema autobirkonfiguragarri izena eman zaie, hain zuzen ere.

Autobirkonfigurazioa egitea konplexua da. *Core-*z oinarritutako sistema multiprozesadore batean ondo egiteko bi gauza beharrezkoak dira: FPGAk birkonfigurazio partzial dinamikoa maila teknologikoan onartzea eta diseinua bera kontrolatzeko sitema bat izatea.

Tesi honek core-etan oinarritutako sistema multiprozesadore autobirkonfigurazioa kontrolatzeko sistema proposatzen du. Hasteko, kontrol-sistemaren planteamendu orokorra egiten da. Honek, txip batean sistema ohikoenen diseinua burutzeko, espezifikazio estandarrak erabiltzen dituzten diseinuetan txertatu ahal izateko balio behar du. Orokortasun hau prozesadore anizkuna den eredu birkonfiguragarrian gauzatzen da eta kontrolaren azpiegituran beharrezkoak diren elementuen ezaugarriak definitzen dira. Diseinu batean, autobirkonfiguarzioaren egokitasuna aztertzeko, azpiegiturak behar dituen baliabideen eredu matematikoa egiten da eta denbora tarteen parametroak neurtzen dira. Aurkeztutako sistema teorikoa teknologia birkonfiguragarri jakin bat erabiliz frogatzen da. Horretarako, birkonfigurazioaren kontrolak duen azpiegituran zehaztutako elementu guztiak burutzen dira eta, horrez gain, multikontestu eta multiprozesadorea duten diseinuak baimentzen dituzten tresna osagarriak sortzen dira.

Azpiegitura hau diseinatutako hiru plataformatan aplikatzen da. Hirurak autobirkonfigurazioa gauzatzeko proposaturiko kontrol sistema probatzeko diseinatuta daude. Saiakera hauek egiteko FPGA-ren konfigurazioa guztiz kontrolatzea onartzen duen prototipo berezia egin behar izan da.

## Resumen

En la actualidad, la densidad de transistores admisible en los dispositivos electrónicos es tal que ya es posible la integración de sistemas digitales completos en un único circuito integrado, son los denominados *System-on-Chips* o SoCs. Con el fin de reducir el tiempo de desarrollo y poder afrontar con éxito este tipo de diseños, habitualmente se componen los mismos a base de módulos o *cores*. Estos módulos, dada su complejidad, incluyen frecuentemente uno o varios procesadores, por lo que, en estos casos, se dispone de sistemas multi-procesador.

Este nivel de integración también se ha extendido a los dispositivos reconfigurables FPGA, siendo esta alternativa una de las más utilizadas dada la flexibilidad que ofrece. Sin embargo, el uso más común de su capacidad de reconfiguración se limita a las fases de prototipado para facilitar la depuración de diseño y, en algunos casos, para realizar posteriores actualizaciones del mismo.

Sin embargo, las FPGAs más recientes admiten que se modifique parte de su configuración mientras el resto del circuito configurado sigue funcionando. Esta capacidad, denominada reconfiguración parcial dinámica, tiene particular interés en los diseños de sistemas digitales mediante módulos en un único circuito integrado. En estos casos, el procesamiento realizado en el *chip*, también puede determinar cambios del contexto para circuitos o programas de los módulos y aplicarlos. Concretamente, el término utilizado para denominar este tipo de diseños es el de sistemas auto-reconfigurables.

La operación de auto-reconfiguración es compleja. Para realizarla con garantías en un sistema multi-procesador basado en *cores*, además de que la FPGA admita la reconfiguración parcial dinámica a nivel tecnológico, es necesario un sistema de control en el propio diseño.

Esta tesis propone un sistema de control de la auto-reconfiguración para sistemas multi-procesador basados en *cores*. Inicialmente, se realiza un planteamiento generalizado del sistema de control, válido para ser incorporado a diseños que utilicen las especificaciones estándar para diseño de sistemas en un *chip* más habituales. Esta generalización se plasma en un modelo reconfigurable multi-procesador, definiéndose a partir del mismo las características de los elementos requeridos en la infraestructura de control. Para facilitar el análisis de la idoneidad de la auto-reconfiguración en un determinado diseño, se realiza un modelado de los recursos necesarios por la infraestructura y se parametrizan los tiempos involucrados en el proceso de reconfiguración.

El sistema teórico presentado se valida utilizando una tecnología reconfigurable concreta. Para ello, se implementan todos los elementos especificados en la infraestructura de control de la reconfiguración y se desarrollan herramientas adicionales que permiten diseños multiprocesador y multi-contexto. Esta infraestructura se aplica sobre tres plataformas diseñadas expresamente para experimentar la auto-reconfiguración con el sistema de control propuesto. Estos ensayos han requerido la construcción de un prototipo especial que admita un control total de los procesos de configuración de la FPGA.

Resumen

## Índice general

| Αŀ | bstract                                                                                                    | ٧        |

|----|------------------------------------------------------------------------------------------------------------|----------|

| La | aburpena                                                                                                   | VI       |

| Re | esumen                                                                                                     | IX       |

| Ta | abla de Acrónimos                                                                                          | XX       |

| I. | Introducción, estado del arte y objetivos                                                                  | 1        |

| 1. | Introducción  1.1. Contexto de la tesis                                                                    | 7        |

| 2. | Sistemas Reconfigurables  2.1. Introducción                                                                | 17<br>24 |

| 3. | Sistemas Auto-Reconfigurables basados en cores sobre FPGAs  3.1. Definición formal de auto-reconfiguración | 34<br>38 |

| 4. | Cores Mixtos 4.1. Integración de pequeños procesadores en cores                                            |          |

| 5. | Análisis de las alternativas para el control de la auto-reconfiguración parcial                            | <br>  60 |

| 6.  | Objetivos                                                             | 73    |

|-----|-----------------------------------------------------------------------|-------|

|     | 6.1. Objetivo general                                                 | . 74  |

|     | 6.2. Objetivos parciales                                              | . 74  |

| 11. | Sistema Tornado                                                       | 77    |

| 7.  | Introducción y justificación                                          | 79    |

| 8.  | Modelo reconfigurable multi-procesador                                | 83    |

| 9.  | Infraestructura de control de reconfiguración                         | 89    |

|     | 9.1. Protocolos de control                                            |       |

|     | <ul><li>9.2. Controlador de reconfiguración: TBC</li></ul>            |       |

| 10  | . Modelado de Tornado                                                 | 103   |

|     | 10.1. Caracterización temporal                                        |       |

|     | 10.2. Modelado de recursos lógicos                                    | . 107 |

| 11  | .Reconfiguración intra-task                                           | 113   |

|     | 11.1. TnP-Cores                                                       |       |

|     | 11.2. Flujo de diseño para reconfiguración intra-task                 | . 116 |

| 12  | . Reconfiguración inter-task                                          | 121   |

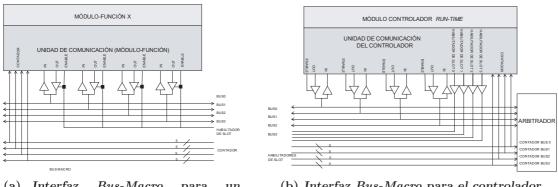

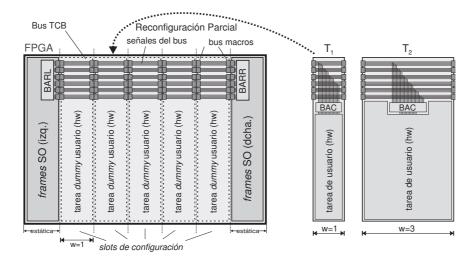

|     | 12.1. Tornado Bus-Macro                                               | . 121 |

|     | 12.2. Flujo de diseño para reconfiguración inter-task                 | . 123 |

| Ш   | . Validación y Evaluación del sistema                                 | 125   |

| 13  | .Plan de pruebas y tecnología                                         | 127   |

|     | 13.1. Plan de pruebas                                                 | . 127 |

|     | 13.2. Reconfiguración parcial dinámica en dispositivos Virtex         | . 127 |

| 14  | . Herramientas hardware                                               | 133   |

|     | 14.1. Especificación estándar para interconexión de IP-Cores Wishbone | . 133 |

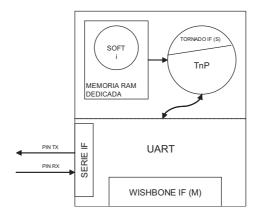

|     | 14.2. Unidad procesadora TnP para Virtex y Wishbone                   |       |

|     | 14.3. Controlador de reconfiguración TBC para Virtex y Wishbone       |       |

|     | 14.4. Módulos parametrizables auxiliares                              | . 148 |

| 15  | . Herramientas software                                               | 149   |

|     | 15.1. Sistema de desarrollo ISE                                       |       |

|     | 15.2. Ensamblador para procesadores TnP                               |       |

|     | 15.3 Scripts de automatización                                        | 153   |

| 16. Plataforma de verificación básica: Video-Multimaster 1        |     |  |  |  |  |

|-------------------------------------------------------------------|-----|--|--|--|--|

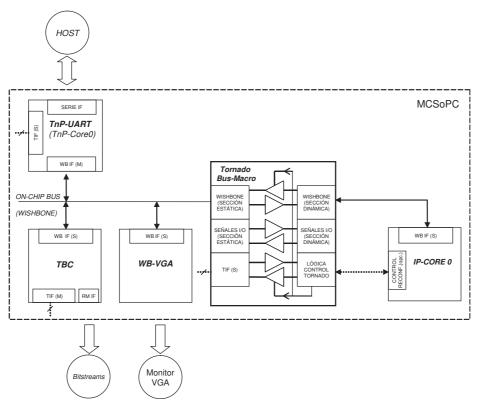

| 16.1. Descripción general                                         |     |  |  |  |  |

| 16.2. Diagrama de bloques                                         |     |  |  |  |  |

| 16.3. Módulos IP                                                  |     |  |  |  |  |

| 16.4. Resultados experimentales                                   |     |  |  |  |  |

| 17. Plataforma de verificación avanzada I: AMT                    | 169 |  |  |  |  |

| 17.1. Descripción general                                         | 169 |  |  |  |  |

| 17.2. Diagrama de bloques                                         |     |  |  |  |  |

| 17.3. Módulos IP                                                  |     |  |  |  |  |

| 17.4. Resultados experimentales                                   |     |  |  |  |  |

| 18. Plataforma de verificación avanzada II: IP-Cores Bajo Demanda |     |  |  |  |  |

| 18.1. Descripción general                                         | 183 |  |  |  |  |

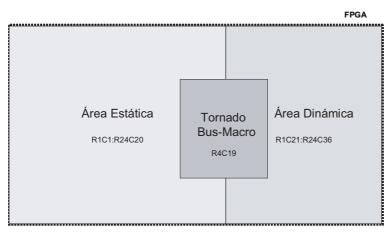

| 18.2. Diagrama de bloques                                         |     |  |  |  |  |

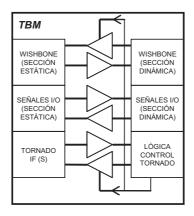

| 18.3. Tornado Bus-Macro                                           |     |  |  |  |  |

| 18.4. Módulos IP dinámicos                                        |     |  |  |  |  |

| 18.5. Módulos IP estáticos                                        |     |  |  |  |  |

| 18.6. Resultados experimentales                                   |     |  |  |  |  |

| IV. Conclusiones y trabajo futuro                                 | 197 |  |  |  |  |

| 19. Conclusiones                                                  | 199 |  |  |  |  |

| 19.1. Principales aportaciones                                    | 200 |  |  |  |  |

| 19.2. Publicaciones generadas a partir de esta Tesis              |     |  |  |  |  |

| 20. Trabajo futuro                                                | 207 |  |  |  |  |

## Índice de figuras

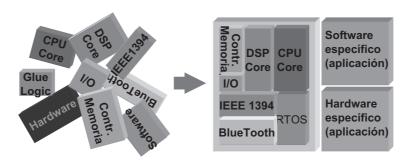

| 1.1.  | Diseño de SoC basado en bloques                                                                                                                             | 5  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

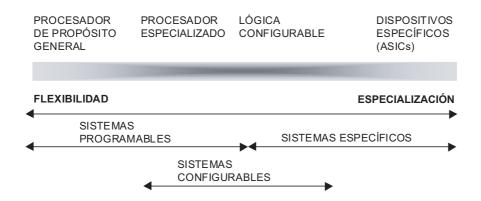

| 2.1.  | Sistemas de computación según el grado de flexibilidad                                                                                                      | 11 |

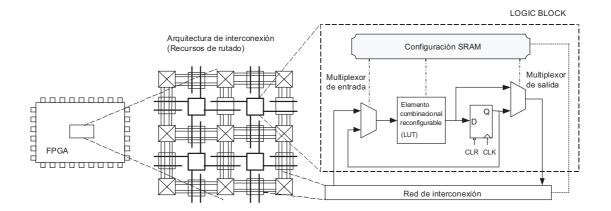

| 2.2.  | Modelo genérico de una FPGA                                                                                                                                 | 13 |

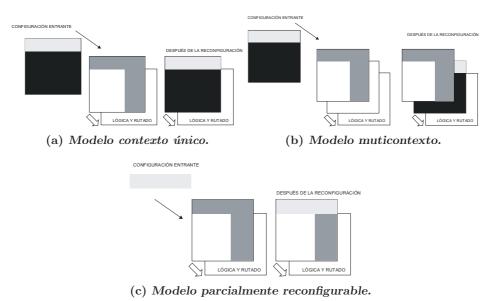

| 2.3.  | Modelos de configuración                                                                                                                                    | 15 |

| 2.4.  | Modelos de reconfiguración dinámica                                                                                                                         | 16 |

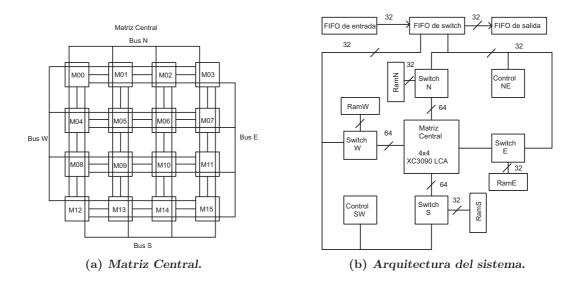

| 2.5.  | Plataforma DECPeRLe-1                                                                                                                                       | 18 |

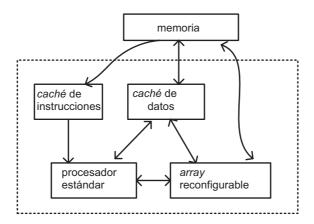

| 2.6.  | Diagrama de bloques del sistema Garp                                                                                                                        | 19 |

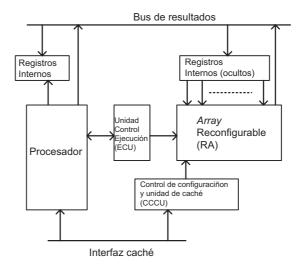

| 2.7.  | Arquitectura simplificada del sistema Chimaera.                                                                                                             | 20 |

| 2.8.  | Procesador Dynamic Instruction Set Computer (DISC)                                                                                                          | 21 |

| 2.9.  | Maia CSoC. Procesador reconfigurable heterogéneo                                                                                                            | 22 |

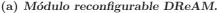

| 2.10. | Dynamically Reconfigurable Architecture for Mobile communication systems                                                                                    |    |

|       | (DReAM) CSoC                                                                                                                                                | 23 |

| 2.11. | CSoC académico/comercial compuesto por un $core$ Leon y $cores$ PAC XPP $^{\mathrm{TM}}$ .                                                                  | 24 |

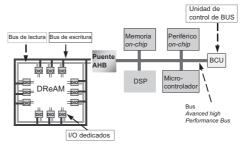

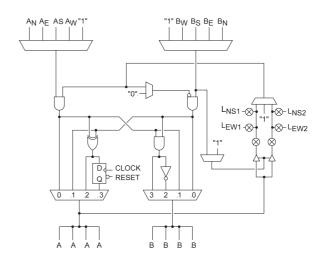

| 2.12. | Configurable Logic Block de Virtex (2 Slices)                                                                                                               | 25 |

| 2.13. | Estructura de la celda de los dispositivos de la serie AT6000 de Atmel                                                                                      | 28 |

| 3.1.  | Gestor de reconfiguración genérico de Shirazi et al                                                                                                         | 33 |

| 3.2.  | Modelo de componente reconfigurable basado en una red estática                                                                                              | 33 |

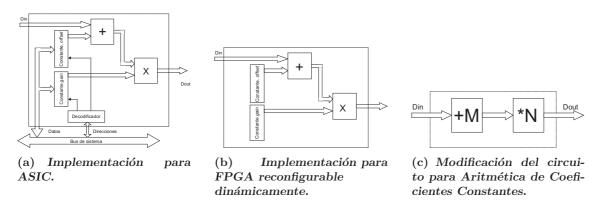

| 3.3.  | Circuito digital para la aplicación de <i>offset</i> y control de ganancia a una señal digital [1]                                                          | 35 |

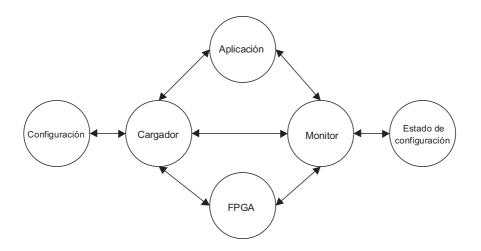

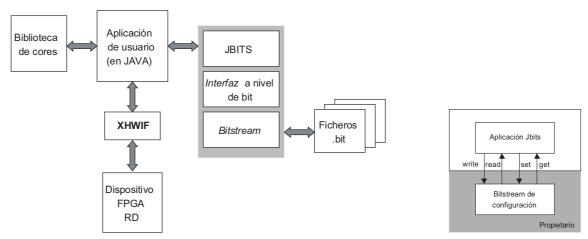

| 3.4.  | Entorno JAVA para soporte de la reconfiguración dinámica                                                                                                    | 36 |

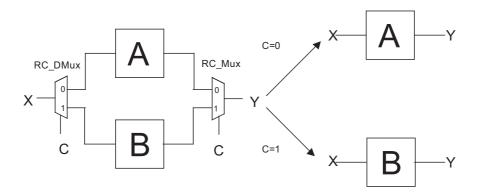

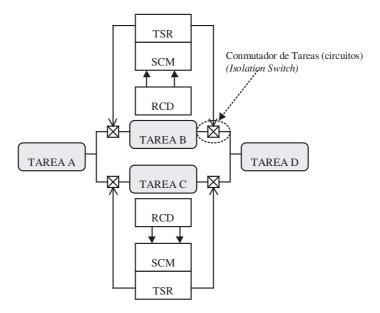

| 3.5.  | Dispositivos virtuales integrados en el diseño para permitir la simulación de lógica reconfigurable dinámicamente. Técnica <i>Dynamic Circuit Switching</i> |    |

|       | (DCS)                                                                                                                                                       | 41 |

| 3.6.  | Modelo de los Programmable Multi-function Cores (PMCs)                                                                                                      | 42 |

| 3.7.  | Aplicación del flujo de diseño mixto de Dyer a cores reconfigurables dinámi-                                                                                |    |

|       | camente                                                                                                                                                     | 44 |

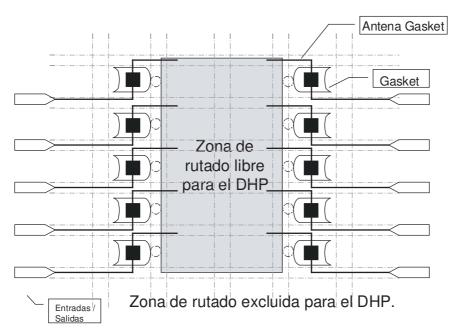

| 3.8.  | Antenas Gasket para la interconexión de DHPs a la zona estática del sistema.                                                                                | 45 |

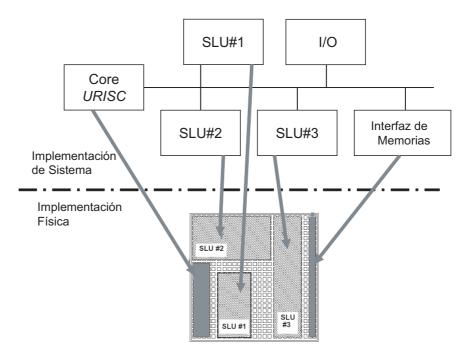

| 3.9.  | Arquitectura de la plataforma Flexible URISC                                                                                                                | 46 |

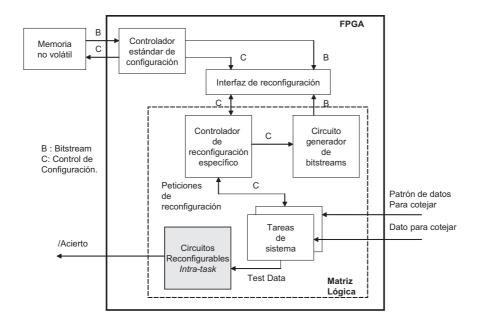

|       | Sistema auto-reconfigurable para la comparación de patrones de datos                                                                                        | 47 |

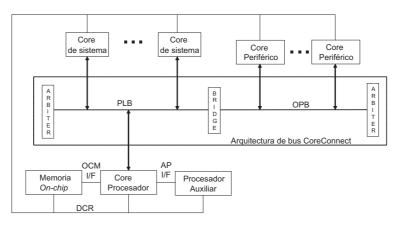

| 3.11. | Tipos de buses en la especificación CoreConnect <sup>TM</sup> de IBM                                                                                        | 50 |

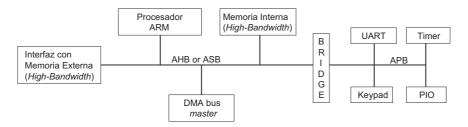

| 3.12. | Tipos de buses en la especificación AMBA de ARM                                                                                                             | 51 |

| 3.13. | Conexión de Cores mediante un único bus Wishbone                                                                                                            | 52 |

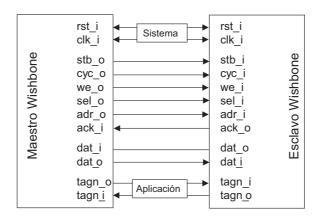

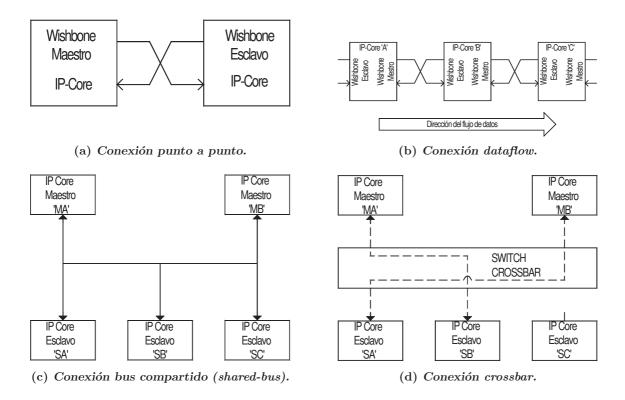

| 3.14. | Topologías de interconexión de bus soportadas por especificación Wishbone                                                                                   | 53 |

| 3.15. | Módulos hardware de la plataforma SRP                                                                                                                       | 54 |

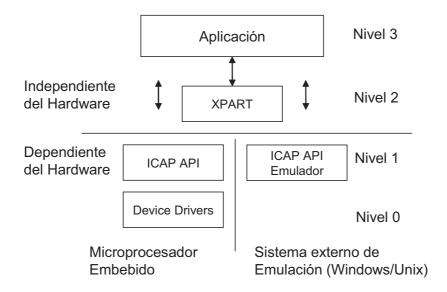

| 3.16. | Niveles software para la plataforma SRP                                                                                                                     | 55 |

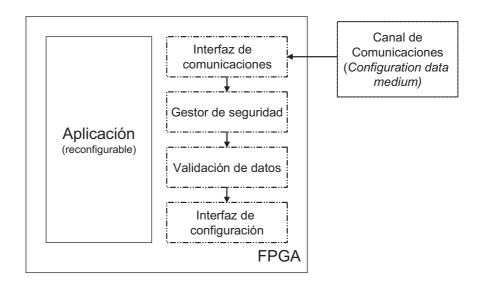

| 3.17.        | Arquitectura del framework para auto-reconfiguración integrado en una FP-                                                                                  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | GA propuesto por Fong et al                                                                                                                                |

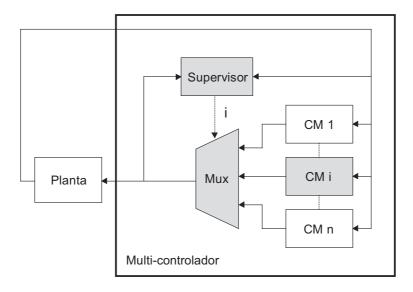

| 3.18.        | Arquitectura Multi-controller                                                                                                                              |

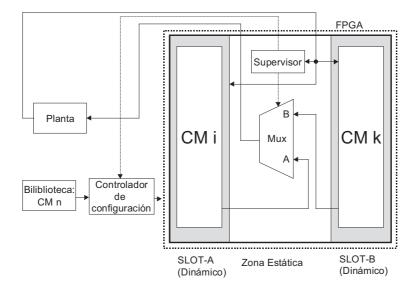

| 3.19.        | Implementación mediante reconfiguración parcial dinámica de la arquitectura<br>Multi-controller                                                            |

| 3.20.        | Bloques principales de modelo de reconfiguración parcial dinámica con gestión de prioridades                                                               |

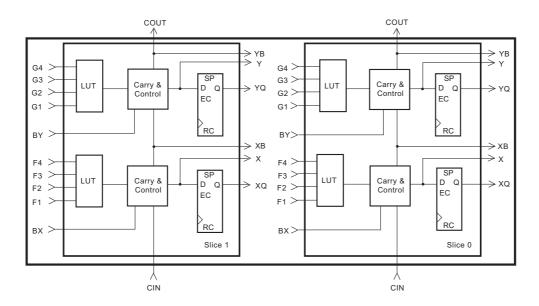

| 3.21         | Bus-Macro para la NoC propuesta en el modelo de Ullmann et al                                                                                              |

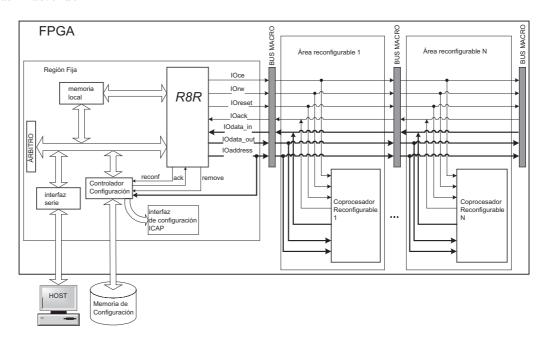

| 3.22.        | Infraestructura general del sistema R8NR (modelo FiPRe) 60<br>Entorno Run-Time para Sistema Operativo para hardware reconfigurable de                      |

|              | H. Walder y M. Platzner                                                                                                                                    |

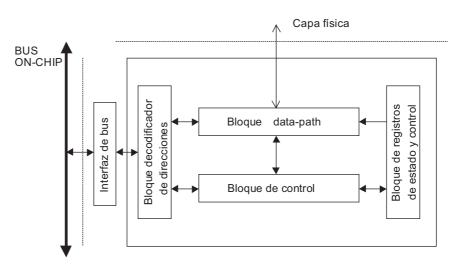

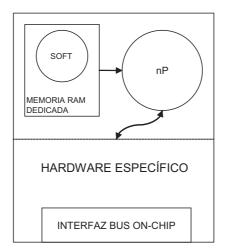

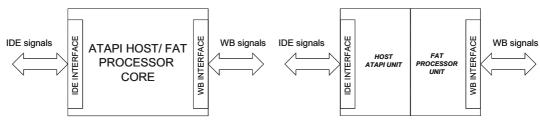

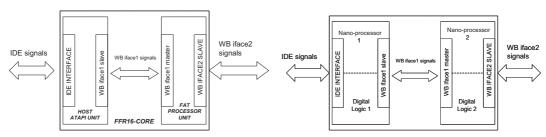

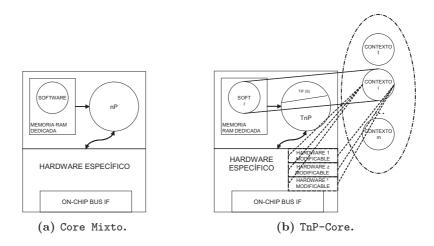

| 4.1.         | Arquitectura de <i>core</i> con nano-procesador embebido (Core Mixto) 65                                                                                   |

| 4.2.         | Core FFR16                                                                                                                                                 |

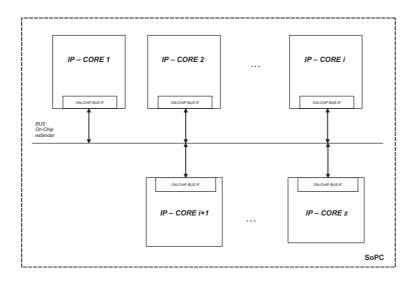

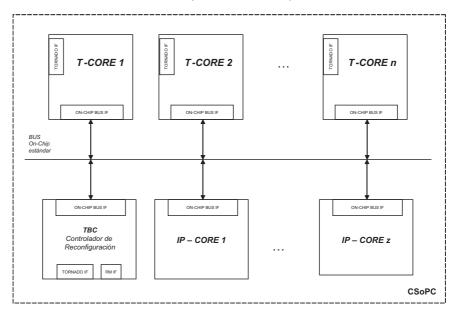

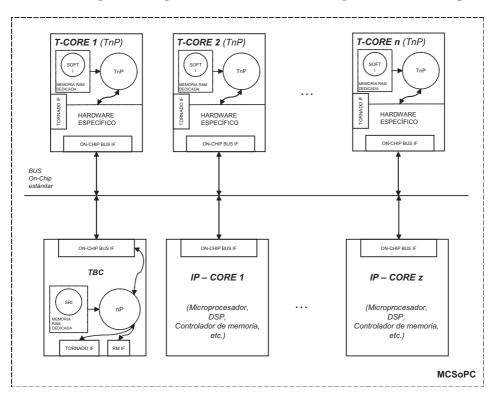

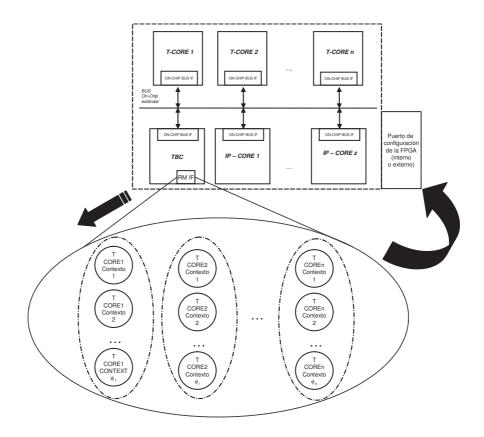

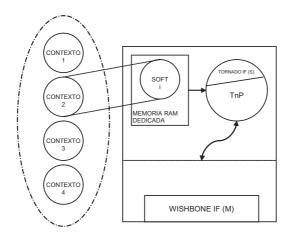

| 8.1.         | Arquitectura generalizada de un SoPC basado en <i>cores</i>                                                                                                |

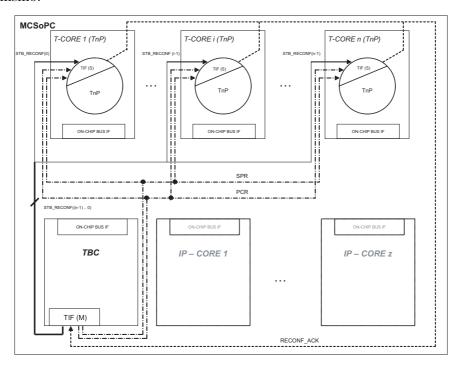

| 8.2.<br>8.3. | Arquitectura generalizada de un <i>Configurable</i> -SoPC compatible Tornado 84 Modelo Tornado: arquitectura generalizada de un CSoPC, compatible Tornado, |

|              | con la posibilidad de integrar Cores Mixtos                                                                                                                |

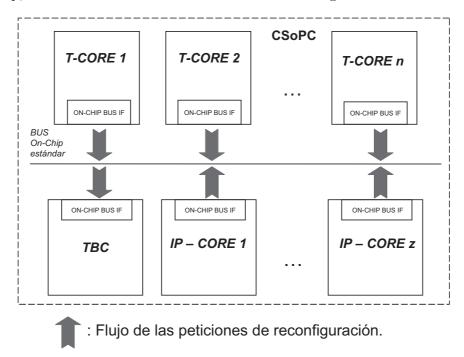

| 9.1.         | Flujo de petición de reconfiguraciones. Diferentes fuentes de solicitud de reconfiguraciones para los T-Cores                                              |

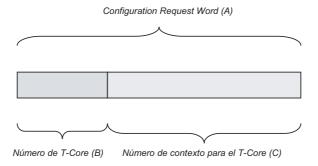

| 9.2.         | Palabra de solicitud de reconfiguración CRW                                                                                                                |

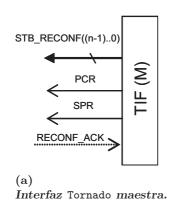

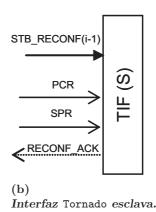

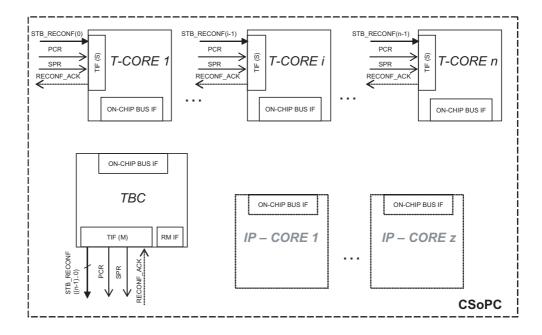

| 9.3.         | Interfaces Tornado                                                                                                                                         |

| 9.4.         | Interfaces Tornado incluidas en los T-Cores y en el controlador de reconfiguración TBC                                                                     |

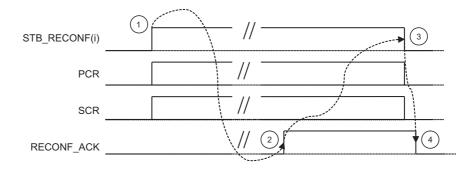

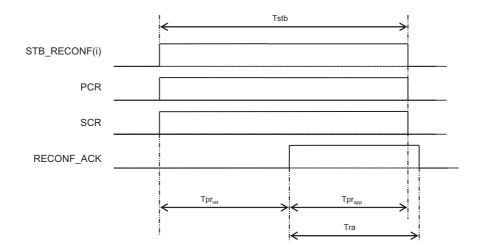

| 9.5.         | Secuencia del handshake para la aplicación de la reconfiguración                                                                                           |

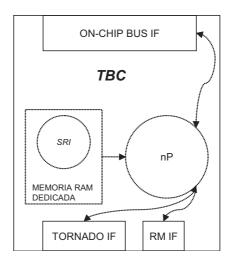

| 9.6.         | Arquitectura del controlador básico de reconfiguración definido en Tornado 98                                                                              |

| 9.7.         | Interfaz RM IF                                                                                                                                             |

| 9.8.         | Interfaces Tornado de los TnPs                                                                                                                             |

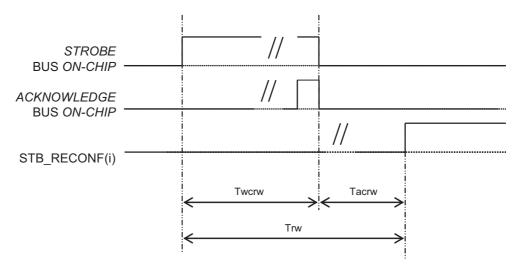

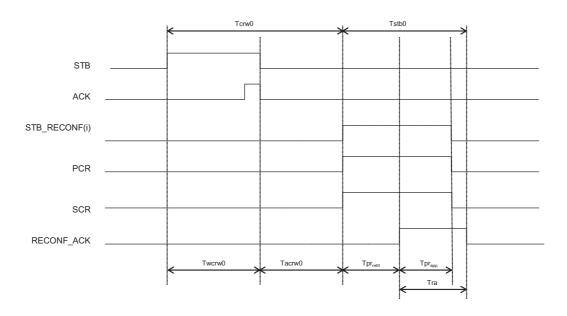

| 10.1.        | Diagrama de tiempos de la escritura y aplicación de una palabra de petición                                                                                |

| 10.0         | de reconfiguración CRW                                                                                                                                     |

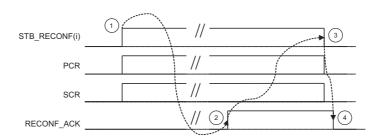

|              | Pasos de la secuencia del <i>handshake</i> de configuración                                                                                                |

|              | Parámetros temporales de la secuencia del <i>handshake</i> de configuración 106                                                                            |

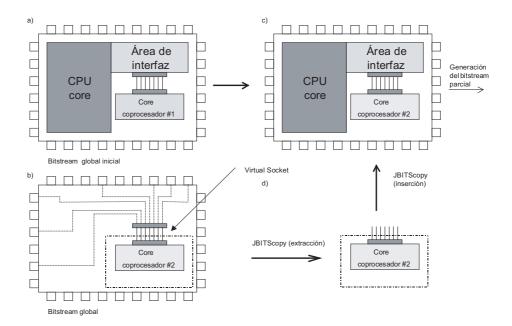

|              | Modificación de los Cores Mixtos                                                                                                                           |

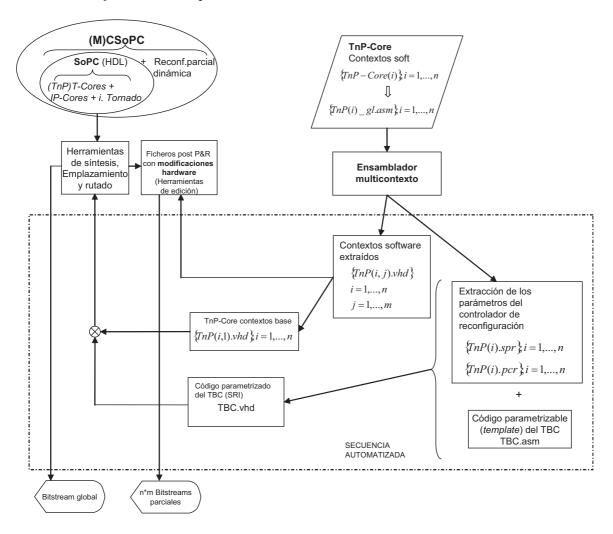

| 11.2.        | Diagrama de flujo de diseño con reconfiguración intra-task                                                                                                 |

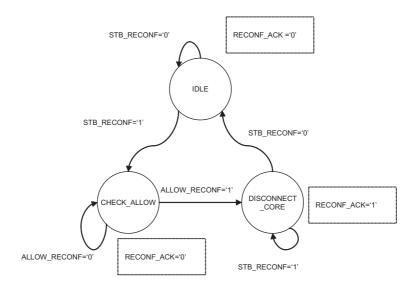

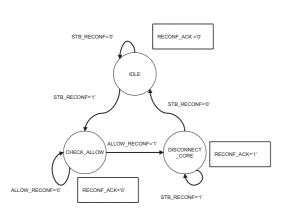

| 12.1.        | Máquina de estados implementada en la Tornado Bus-Macro                                                                                                    |

| 12.2.        | Diagrama de flujo de diseño con reconfiguración inter-task                                                                                                 |

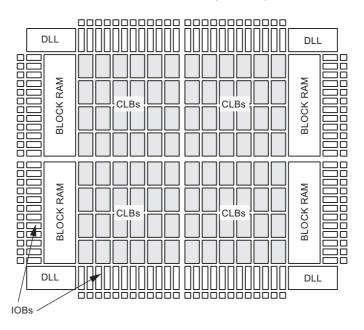

| 13.1.        | Distribución de los recursos lógicos en el dispositivo más pequeño de la familia Spartan-II                                                                |

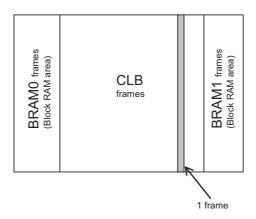

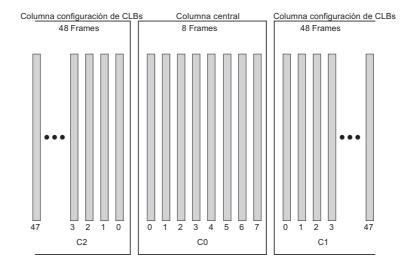

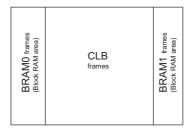

| 13 9         | Distribución de los diferentes tipos de frames en un dispositivo Virtex 129                                                                                |

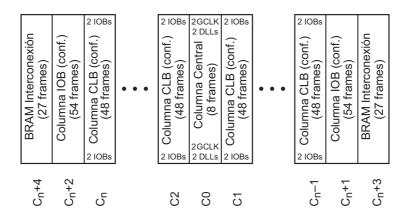

|              | Distribución de las frame columns en la memoria de configuración                                                                                           |

|              | Distribución de los frames en los frame columns                                                                                                            |

|              |                                                                                                                                                            |

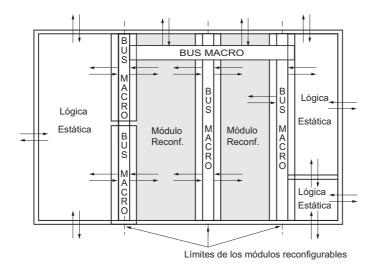

| 13.5. | Conexión entre módulos reconfigurables para aplicar reconfiguración <i>inter-</i><br>task en dispositivos Virtex de Xilinx   | 131 |

|-------|------------------------------------------------------------------------------------------------------------------------------|-----|

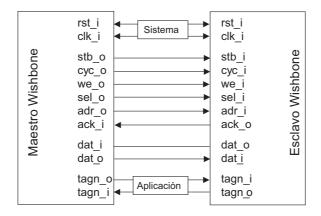

| 14.1. | Conexión de <i>Cores</i> mediante un único bus Wishbone                                                                      | 135 |

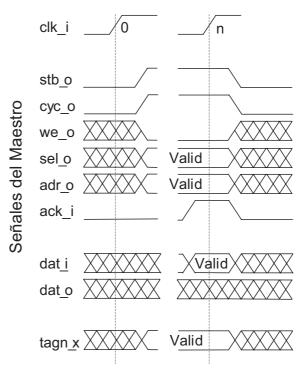

|       | Ciclo de lectura simple en Wishbone                                                                                          |     |

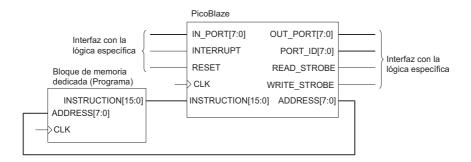

|       | Unidad procesadora <i>Picoblaze</i>                                                                                          |     |

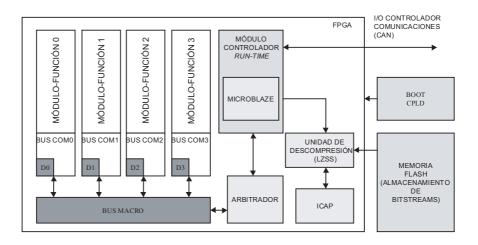

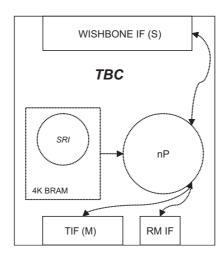

|       | Arquitectura del TBC para dispositivos Virtex y compatible Wishbone                                                          |     |

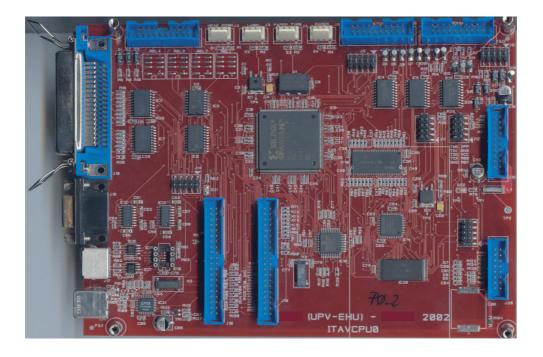

|       | Prototipo desarrollado para la experimentación con reconfiguración parcial dinámica.                                         |     |

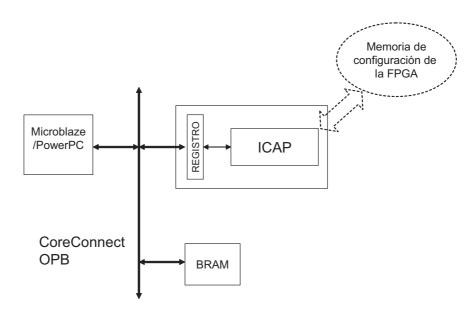

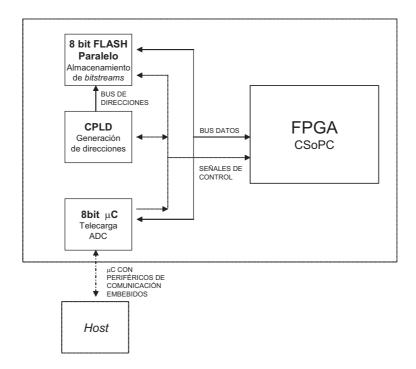

| 14.6. | Subsistema de carga de <i>bitstreams</i> parciales y totales integrado en el prototipo                                       |     |

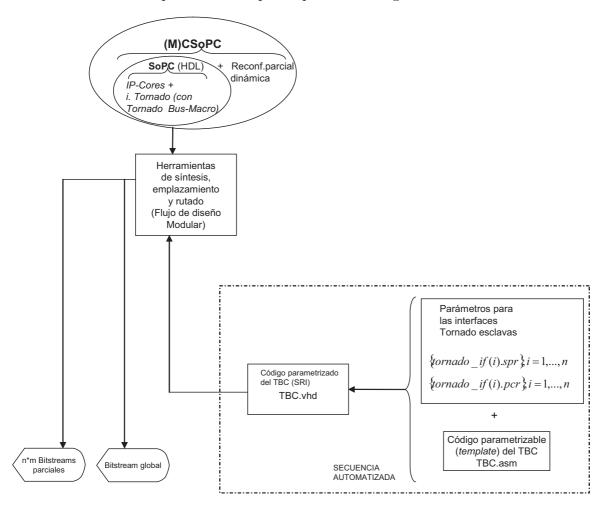

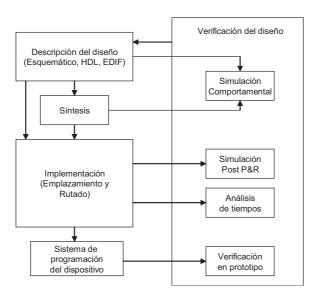

| 15.1. | Flujo de diseño ISE                                                                                                          | 149 |

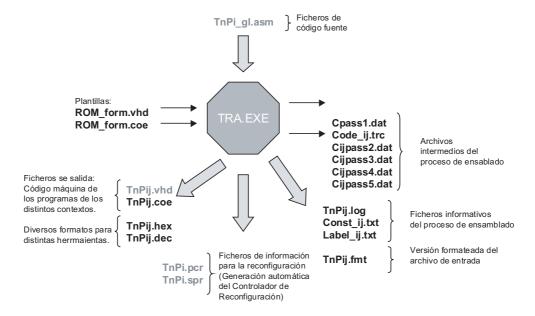

| 15.2. | Diagrama de flujo de ficheros del ensamblador TRA para un TnP                                                                | 152 |

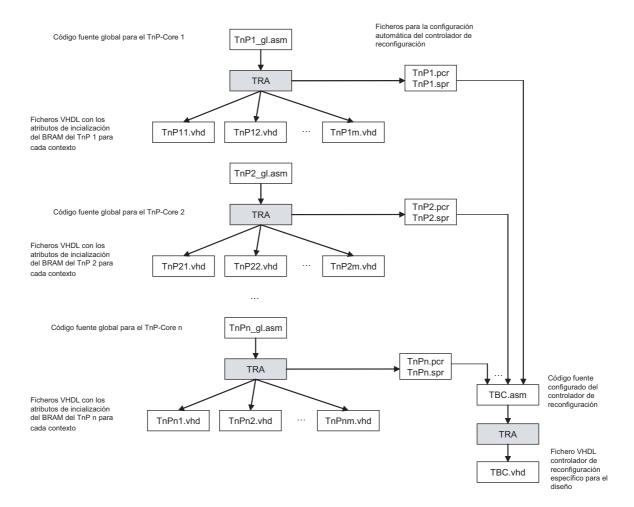

| 15.3. | Generación automática de los ficheros VHDL para la inicialización de los bloques de RAM y del controlador de reconfiguración | 154 |

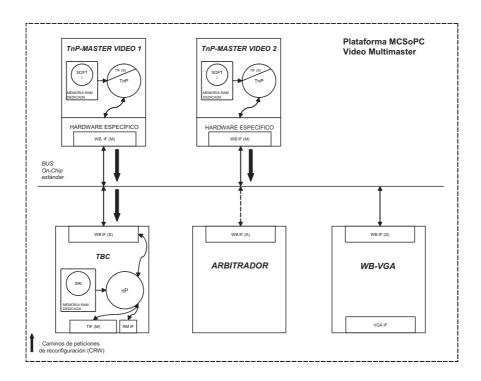

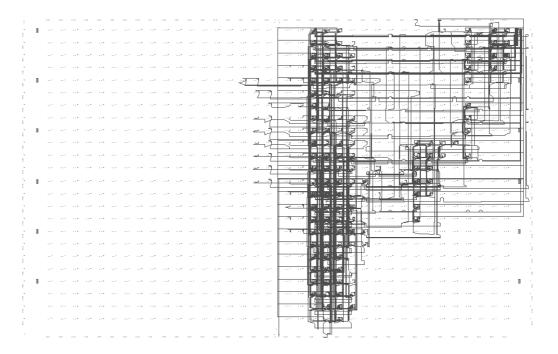

| 16.1  | Diagrama de bloques de la plataforma de verificación <i>Video-Multimaster</i>                                                | 156 |

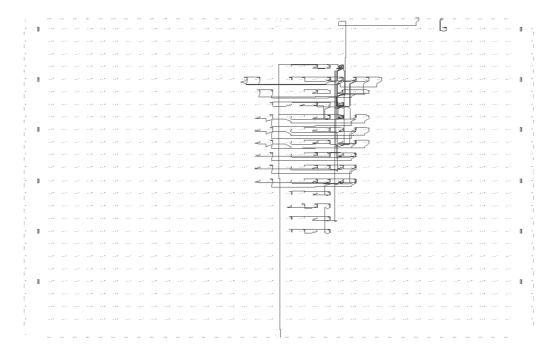

|       | TnP-Master Video core                                                                                                        |     |

|       | Sistema de visualización de la actividad en los TnP-Master Video mediante                                                    | 101 |

|       | un monitor seccionado                                                                                                        | 158 |

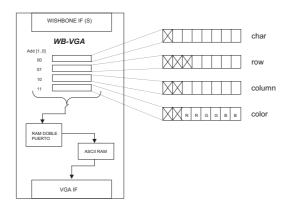

| 16.4. | WB-VGA core                                                                                                                  |     |

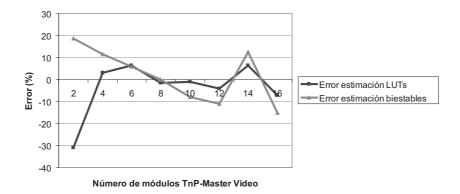

|       | Evolución del error en las estimaciones de recursos lógicos en función de la                                                 |     |

|       | complejidad de la plataforma                                                                                                 | 163 |

| 16.6. | Parámetros temporales normalizados.                                                                                          |     |

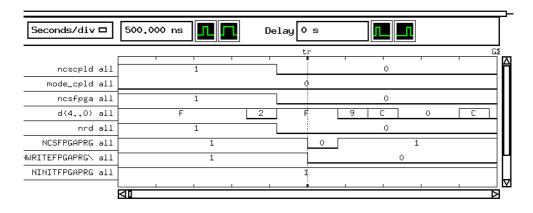

|       | Carga de un bistream parcial controlada por el TBC                                                                           |     |

|       | Distribución de los BRAM frames en un dispositivo Virtex con dos columnas                                                    |     |

|       | de BRAMs                                                                                                                     | 166 |

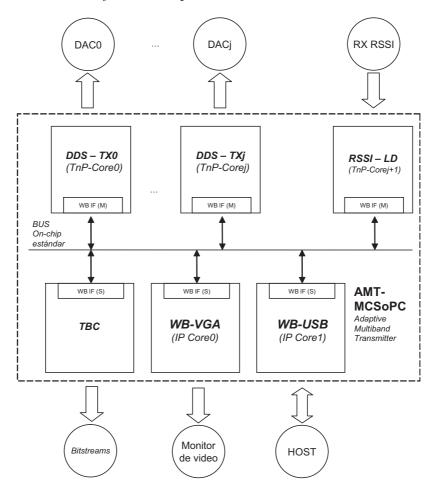

| 17.1. | Plataforma AMT desarrollada para la evaluación del sistema Tornado                                                           | 170 |

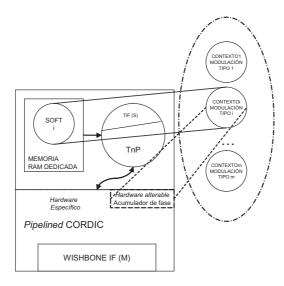

| 17.2. | Partición interna del TnP-Cores DDS-TXi                                                                                      | 171 |

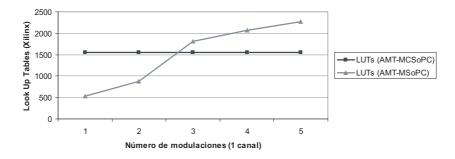

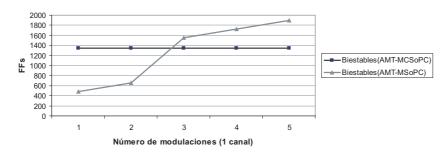

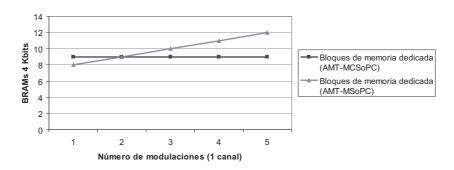

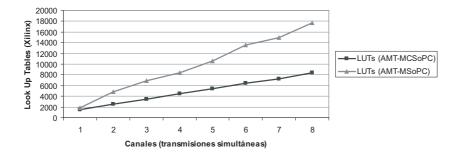

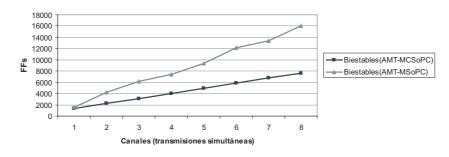

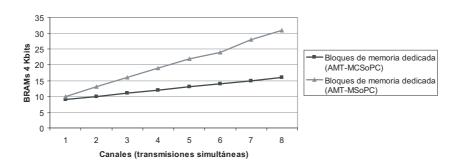

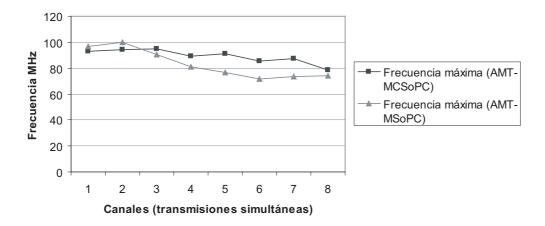

| 17.3. | Comparativa de la utilización de recursos lógicos entre plataformas AMT de                                                   |     |

|       | un único canal con Tornado y sin Tornado.                                                                                    | 177 |

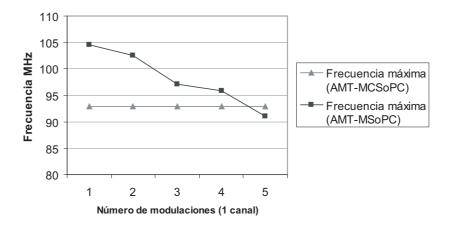

| 17.4. | Evolución de la frecuencia máxima de funcionamiento para el conjunto de                                                      |     |

|       | plataformas AMT de un canal                                                                                                  |     |

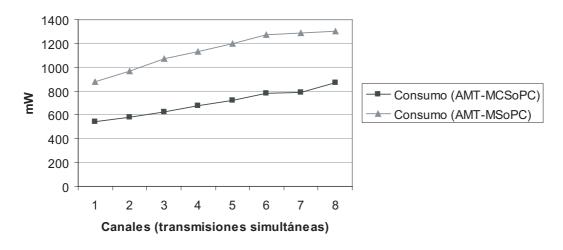

| 17.5. | ${\bf Comparativa\ de\ la\ utilizaci\'on\ de\ recursos\ l\'ogicos\ entre\ plataformas\ {\tt AMT\ MCSoPer}}$                  |     |

|       | y MSoPC de distinto número de canales y tres tipos de modulación                                                             | 179 |

| 17.6. | Plataformas AMT MCSoPC y MSoPC con distintos número de canales y tres                                                        |     |

|       | tipos de modulaciones                                                                                                        | 181 |

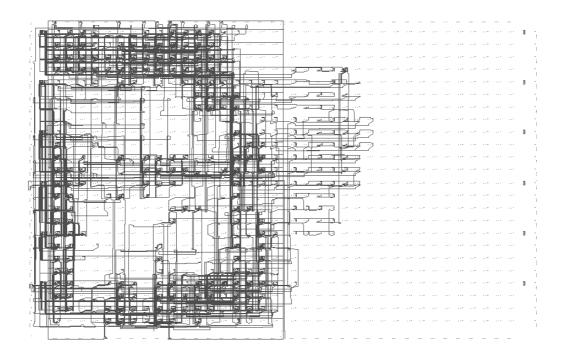

| 18.1. | Plataforma experimental IP-Cores bajo demanda                                                                                | 185 |

|       | TBM para Spartan-II y Wishbone                                                                                               |     |

|       | Lógica de control integrada en la TBM                                                                                        |     |

|       | Circuito interno de la TBM                                                                                                   |     |

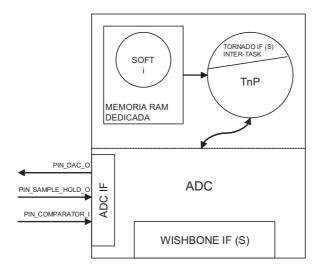

|       | Arquitectura del WB_ADC_dynamic_core                                                                                         |     |

|       | Módulo dinámico WB_ADC_dynamic_core emplazado y rutado                                                                       |     |

|       | Módulo dinámico WB_mult_dynamic_core emplazado y rutado                                                                      |     |

| 18.8. | Módulos estáticos agrupados, emplazados y rutados                                                                            | 194 |

|       |                                                                                                                              |     |

| Índice de figuras                |      |      |     |

|----------------------------------|------|------|-----|

| 18.9. Arquitectura del TnP-UART. | <br> | <br> | 194 |

## Índice de tablas

| 0.1.  | Tabla de Acrónimos                                                                                                                                    | XXI  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1.  | Resumen de los Sistemas Reconfigurables presentados                                                                                                   | 29   |

| 3.1.  | Especificaciones para interconexión de $cores$ y sus licencias de utilización                                                                         | 49   |

| 4.1.  | Coste de implementación de un sistema de computación ATA+FAT para distintas alternativas SoPC                                                         | 67   |

| 5.1.  | Comparación entre las alternativas actuales para la aplicación de Reconfiguración Parcial Dinámica a plataformas FPGA comerciales basadas en IP-Cores | . 71 |

| 7.1.  | Términos utilizados en el sistema Tornado                                                                                                             | 82   |

| 8.1.  | Características generales de los controladores de reconfiguración de las diferentes propuestas                                                        | 85   |

| 13.1. | . Plan de Pruebas                                                                                                                                     | 128  |

| 14.1. | . Juego de instrucciones del nano-procesador soft TnP                                                                                                 | 140  |

|       | . Resultados de implementación de un nano-procesador TnP                                                                                              |      |

|       | . Parámetros de modelado del TnP                                                                                                                      |      |

| 14.4. | . Resultados de implementación del controlador de reconfiguración TBC                                                                                 | 147  |

| 14.5. | . Parámetros de modelado del TBC                                                                                                                      | 147  |

| 16.1. | . Resultados de implementación del core TnP-Master Video en un dispositivo XC2S150                                                                    | 158  |

| 16.2. | Estimaciones del coste en recursos área de Tornado para distintas variantes de la plataforma Video-Multimaster.                                       |      |

| 16.3. | . Resultados de implementar las variantes de la plataforma Video-Multimaster sin infraestructura Tornado                                              |      |

| 16.4. | . Resultados de implementar las variantes de la plataforma Video-Multimaster con la infraestructura de Tornado.                                       |      |

| 16.5. | . Recursos lógicos reales y estimados de la infraestructura Tornado                                                                                   |      |

|       | . Valores normalizados de los parámetros temporales para la plataforma Video Multi-master                                                             |      |

| 16 7  | Tiempos no normalizados para las plataformas Video-Multimaster                                                                                        | 165  |

## Índice de tablas

| 17.1. Resultados de implementación del TnP-Core DDS-TXi sobre una FPGA Spartan-II                |

|--------------------------------------------------------------------------------------------------|

| X2S150-6                                                                                         |

| 17.2. Resultados de implementación del TnP-Core RSSI-LD en una FPGA Spartan-                     |

| II X2S150                                                                                        |

| $17.3.$ Valores normalizados de los parámetros temporales para la plataforma ${\tt AMT}$ . $178$ |

| 18.1. Valores normalizados de los parámetros temporales para la plataforma IP-Cores              |

| bajo demanda                                                                                     |

## Tabla de Acrónimos

Tabla 0.1.: Tabla de Acrónimos

| Acrónimo             | Término                                                                  |

|----------------------|--------------------------------------------------------------------------|

| ADC                  | Analog to Digital Converter                                              |

| AHB                  | Advanced High speed Bus                                                  |

| ALU                  | Arithmetic Logic Unit                                                    |

| AMT                  | Adaptive Multi-Transmitter                                               |

| APB                  | Advanced Peripheral Bus                                                  |

| API                  | Application Program Interface                                            |

| ASIC                 | Application Specific Integrated Circuit                                  |

| ASP                  | Advanced general purpose System Bus                                      |

| ASSP                 | Application-Specific Standar Product                                     |

| BRAM                 | $\operatorname{BlockRAM}$                                                |

| CCCU                 | Configuration Control Cache Unit                                         |

| CLB                  | Configurable Logic Block                                                 |

| CM                   | Core Mixto                                                               |

| CMOS                 | Complementary Metal-Oxide Semiconductor                                  |

| CPLD                 | Complex Programmable Logic Device                                        |

| CPU                  | Central Processing Unit                                                  |

| $\operatorname{CRW}$ | Configuration Request Word                                               |

| CSoC                 | Configurable-Systems-on-Chips                                            |

| CSoPC                | Configurable-System-On-Programable-Chip                                  |

| DAC                  | Digital to Analog Converter                                              |

| DCM                  | Digital Clock Management                                                 |

| DCR                  | Device Control Register                                                  |

| DCS                  | Dynamic Circuit Switching                                                |

| DDS                  | Direct Digital Synthesis                                                 |

| DHP                  | Dynamic Hardware Plugin                                                  |

| DISC                 | Dynamic Instruction Set Computer                                         |

| $\operatorname{DLL}$ | Delay-Locked Loop                                                        |

| DReAM                | Dynamically Reconfigurable Architecture for Mobile communication systems |

| DRIP                 | Dynamically Reconfigurable IP                                            |

| ECU                  | Execution Control Unit                                                   |

| FFR16                | First File Reader FAT16                                                  |

| FIP Flexible Instruction Processor FPGA Field Programmable Gate Array FPSLIC Field Programmable System Level Integrated Circuit FPU FAT Processor Unit FPX Field Programmable Port eXtender FSK Frequency Shift Keying GF Galois Field GPL General Public License HAU Host ATAPI Unit HDL Hardware Description Languaje IDE Integrated Device Electronic IOB Input-Output-Block IP-Core Intellectual Proprietary Core ISA Industry Standard Architecture LB Logic Block LHM Linear Hardware Model LUT Look-Up Table MAC Media Access Controller MCSoPC Multiprocessor-Configurable-System-On-Programable-Chip MIPS Million Instructions Per Second MPEG-2 Motion Picture Expert Group -2 NoC Network-on-Chip OCIDEC Open Core IDE Controller OOK On-Off Keying OPB On-chip Peripheral Bus OSCI Open SystemC Initiative PA Processing Array PAE Processing Array PAE Processing Array Element PAL Programmable Array Logic PCI Peripheral Component Interconnect PCR Program Counter Reset PIO Peripheral Input-Output PLB Processor Local Bus PMC Programmable Multifunction Core PSK Phase Shift Keying RA Reconfigurable Array RAM Random Access Memory RCD Reconfigurable Functional Unit RISC Reduced Instruction Set Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | FIFO           | First In - First Out                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------|

| FPGA FPSLIC FPSLIC FIEID Programmable System Level Integrated Circuit FPU FAT Processor Unit FPX Field Programmable Port eXtender FSK Frequency Shift Keying GF Galois Field GPL General Public License HAU Host ATAPI Unit HDL Hardware Description Languaje IDE Integrated Device Electronic IOB Input-Output-Block IP-Core IISA Industry Standard Architecture LB Logic Block LHM Linear Hardware Model LUT Look-Up Table MAC Media Access Controller MCSOPC Multiprocessor-Configurable-System-On-Programable-Chip MIPS Million Instructions Per Second MPEG-2 NoC Network-on-Chip OCIDEC OOK On-Off Keying OPB On-chip Peripheral Bus OSCI Open SystemC Initiative PA Processing Array PAE PAE Processing Array PAE PAI Programmable Array Logic PCI Peripheral Component Interconnect PCR Programmable Multifunction Core PSK Phase Shift Keying RA RA Random Access Memory RCD RECONIGNICAL Unit Reconfigurable Functional Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |                                                        |

| FPSLIC FPU FAT Processor Unit FPX Field Programmable Port eXtender FSK FSK Frequency Shift Keying GF GBPL General Public License HAU Host ATAPI Unit HDL Hardware Description Languaje IDE Integrated Device Electronic IOB Input-Output-Block IP-Core ISA Industry Standard Architecture LB LUT MAC Media Access Controller MCSoPC MIPS Million Instructions Per Second MPEG-2 NoC ONC ON-Off Keying OPB ON-chip Peripheral Bus OSCI OPB OSCI OPB OSCI OPB OSCI OPB OSCI OPB OSCI OPE PAA Processing Array PAE PAL PROGRAM PAA PROCESSOR POR POR POR POR POR POR POR POR POR P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                                                        |

| FPU FAT Processor Unit FPX Field Programmable Port eXtender FSK Frequency Shift Keying GF Galois Field GPL General Public License HAU Host ATAPI Unit HDL Hardware Description Languaje IDE Integrated Device Electronic IOB Input-Output-Block IP-Core Intellectual Proprietary Core ISA Industry Standard Architecture LB Logic Block LHM Linear Hardware Model LUT Look-Up Table MAC Media Access Controller MCSoPC MITS Million Instructions Per Second MPEG-2 Motion Picture Expert Group -2 NoC Network-on-Chip OCIDEC Open Core IDE Controller OOK On-Off Keying OPB On-chip Peripheral Bus OSCI Open SystemC Initiative PA Processing Array PAE Processing Array Element PAL Programmable Array Logic PCI Peripheral Component Interconnect PCR Program Counter Reset PIO Peripheral Input-Output PLB Processor Local Bus PMC Programmable Multifunction Core PSK Phase Shift Keying RAA Reconfigurable Functional Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                                                        |

| FPX FSK Frequency Shift Keying GF GAlois Field GPL General Public License HAU HOST ATAPI Unit HDL HARDWARE Description Languaje IDE IDE INTERPRETED IN |                |                                                        |

| FSK GF Galois Field GPL General Public License HAU Host ATAPI Unit HDL Hardware Description Languaje IDE Integrated Device Electronic IOB Input-Output-Block IP-Core Intellectual Proprietary Core ISA Industry Standard Architecture LB Logic Block LHM Linear Hardware Model LUT Look-Up Table MAC Media Access Controller MCSoPC Multiprocessor-Configurable-System-On-Programable-Chip MIPS Million Instructions Per Second MPEG-2 Motion Picture Expert Group -2 NoC Network-on-Chip OCIDEC Open Core IDE Controller OOK On-Off Keying OPB On-chip Peripheral Bus OSCI Open SystemC Initiative PA Processing Array PAE Processing Array Element PAL Programmable Array Logic PCI Peripheral Component Interconnect PCR Program Counter Reset PIO Peripheral Input-Output PLB Programmable Multifunction Core PSK Phase Shift Keying RAM Random Access Memory RCD Reconfigurable Functional Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |                                                        |

| GF GPL GPL General Public License HAU Host ATAPI Unit HDL HIL HIL HIL HIL HIL HIL HIL HIL HIL HI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |                                                        |

| GPL HAU HOST ATAPI Unit HDL HIARDWAYE Description Languaje IDE IDE INTEGRATED INTEGRATED DEVICE Electronic IOB INPUT-Output-Block IIP-Core ISA INDUSTRY Standard Architecture INDUSTRY Standard Architec |                |                                                        |

| HAU Hardware Description Languaje IDE Integrated Device Electronic IOB Input-Output-Block IIP-Core Intellectual Proprietary Core ISA Industry Standard Architecture LB Logic Block LHM Linear Hardware Model LUT Look-Up Table MAC Media Access Controller MCSoPC Multiprocessor-Configurable-System-On-Programable-Chip MIPS Million Instructions Per Second MPEG-2 Motion Picture Expert Group -2 NoC Network-on-Chip OCIDEC Open Core IDE Controller OOK On-Off Keying OPB On-chip Peripheral Bus OSCI Open SystemC Initiative PA Processing Array PAE Processing Array Element PAL Programmable Array Logic PCI Peripheral Component Interconnect PCR Program Counter Reset PIO Peripheral Input-Output PLB Processor Local Bus PMC Programmable Multifunction Core PSK Phase Shift Keying RA Reconfigurable Array RAM Random Access Memory RCD Reconfigurable Functional Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                | General Public License                                 |

| HDL Integrated Device Electronic IOB Input-Output-Block IP-Core Intellectual Proprietary Core ISA Industry Standard Architecture LB Logic Block LHM Linear Hardware Model LUT Look-Up Table MAC Media Access Controller MCSoPC Multiprocessor-Configurable-System-On-Programable-Chip MIPS Million Instructions Per Second MPEG-2 Motion Picture Expert Group -2 NoC Network-on-Chip OCIDEC Open Core IDE Controller OOK On-Off Keying OPB On-chip Peripheral Bus OSCI Open System Initiative PA Processing Array PAE Processing Array Element PAL Programmable Array Logic PCI Peripheral Component Interconnect PCR Program Counter Reset PIO Peripheral Input-Output PLB Processor Local Bus PMC Programmable Multifunction Core PSK Phase Shift Keying RA Reconfigurable Array RAM Random Access Memory RCD Reconfiguration Condition Detector RFU Reconfigurable Functional Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $_{ m HAU}$    |                                                        |

| IDE Integrated Device Electronic IOB Input-Output-Block IIP-Core Intellectual Proprietary Core ISA Industry Standard Architecture LB Logic Block LHM Linear Hardware Model LUT Look-Up Table MAC Media Access Controller MCSoPC Multiprocessor-Configurable-System-On-Programable-Chip MIPS Million Instructions Per Second MPEG-2 Motion Picture Expert Group -2 NoC Network-on-Chip OCIDEC Open Core IDE Controller OOK On-Off Keying OPB On-chip Peripheral Bus OSCI Open SystemC Initiative PA Processing Array PAE Processing Array Element PAL Programmable Array Logic PCI Peripheral Component Interconnect PCR Program Counter Reset PIO Peripheral Input-Output PLB Processor Local Bus PMC Programmable Multifunction Core PSK Phase Shift Keying RA Reconfigurable Array RAM Random Access Memory RCD Reconfigurable Functional Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $\mathrm{HDL}$ | Hardware Description Languaje                          |

| IOB IP-Core IP-Core ISA Intellectual Proprietary Core ISA Industry Standard Architecture LB Logic Block LHM Linear Hardware Model LUT Look-Up Table MAC Media Access Controller MCSoPC MIPS Million Instructions Per Second MPEG-2 NoC OCIDEC OOK OPP OOR OPP OOR OPP OOR OPP OPP OOR OPP OOR OPP OOR OPP OOR OPP OOR OPP OOR OOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | IDE            |                                                        |

| IP-Core ISA Industry Standard Architecture LB Logic Block LHM Linear Hardware Model LUT Look-Up Table MAC Media Access Controller MCSoPC MIltiprocessor-Configurable-System-On-Programable-Chip MIPS Million Instructions Per Second MPEG-2 NoC Network-on-Chip OCIDEC OOK On-Off Keying OPB On-chip Peripheral Bus OSCI Open SystemC Initiative PA Processing Array PAE Processing Array Element PAL Programmable Array Logic PCI Peripheral Component Interconnect PCR Program Counter Reset PIO Peripheral Input-Output PLB Processor Local Bus PMC Programmable Array RAM Random Access Memory RCD Reconfiguration Condition Detector RFU Reconfigurable Functional Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IOB            | 9                                                      |

| ISA Logic Block  LHM Linear Hardware Model  LUT Look-Up Table  MAC Media Access Controller  MCSoPC Multiprocessor-Configurable-System-On-Programable-Chip  MIPS Million Instructions Per Second  MPEG-2 Motion Picture Expert Group -2  NoC Network-on-Chip  OCIDEC Open Core IDE Controller  OOK On-Off Keying  OPB On-chip Peripheral Bus  OSCI Open SystemC Initiative  PA Processing Array Element  PAL Programmable Array Logic  PCI Peripheral Component Interconnect  PCR Program Counter Reset  PIO Peripheral Input-Output  PLB Processor Local Bus  PMC Programmable Multifunction Core  PSK Phase Shift Keying  RA Reconfigurable Array  RAM Random Access Memory  RCD Reconfiguration Condition Detector  RFU Reconfigurable Functional Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IP-Core        |                                                        |

| LHM Linear Hardware Model LUT Look-Up Table MAC Media Access Controller  MCSoPC Multiprocessor-Configurable-System-On-Programable-Chip MIPS Million Instructions Per Second  MPEG-2 Motion Picture Expert Group -2 NoC Network-on-Chip  OCIDEC Open Core IDE Controller  OOK On-Off Keying  OPB On-chip Peripheral Bus  OSCI Open SystemC Initiative PA Processing Array  PAE Processing Array Element  PAL Programmable Array Logic  PCI Peripheral Component Interconnect  PCR Program Counter Reset  PIO Peripheral Input-Output  PLB Processor Local Bus  PMC Programmable Multifunction Core  PSK Phase Shift Keying  RAA Reconfigurable Array  RAM Random Access Memory  RCD Reconfiguration Condition Detector  RFU Reconfigurable Functional Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ISA            |                                                        |

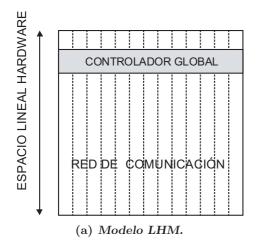

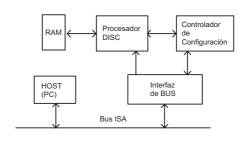

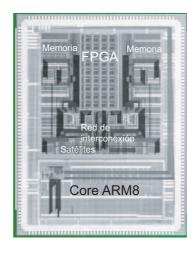

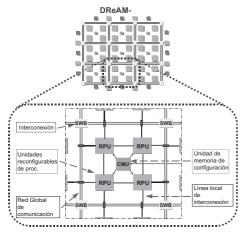

| LUTLook-Up TableMACMedia Access ControllerMCSoPCMultiprocessor-Configurable-System-On-Programable-ChipMIPSMillion Instructions Per SecondMPEG-2Motion Picture Expert Group -2NoCNetwork-on-ChipOCIDECOpen Core IDE ControllerOOKOn-Off KeyingOPBOn-chip Peripheral BusOSCIOpen SystemC InitiativePAProcessing ArrayPAEProcessing Array ElementPALProgrammable Array LogicPCIPeripheral Component InterconnectPCRProgram Counter ResetPIOPeripheral Input-OutputPLBProcessor Local BusPMCProgrammable Multifunction CorePSKPhase Shift KeyingRAReconfigurable ArrayRAMRandom Access MemoryRCDReconfiguration Condition DetectorRFUReconfigurable Functional Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $_{ m LB}$     | Logic Block                                            |